先上一个听来的段子:

—“二维材料好像很热门,有什么实际应用呢?”

—“用途很多,目前主要用于制造博士……”

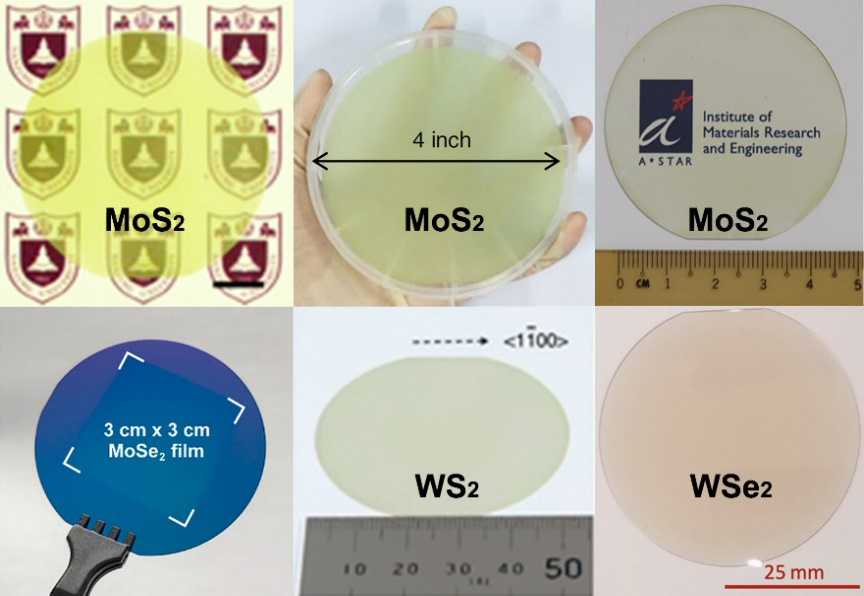

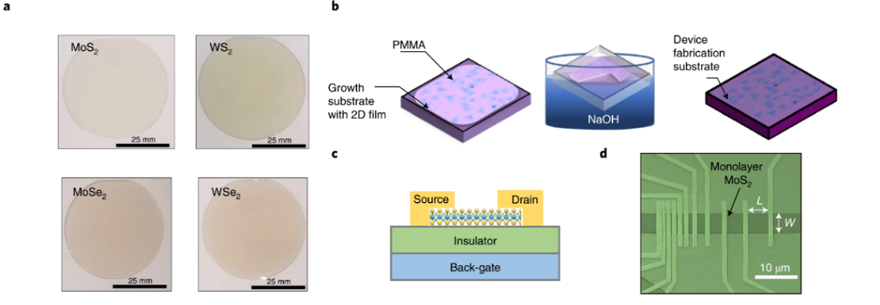

先不管段子好不好笑,二维材料大受追捧确是事实。尤其是在集成电路和电子器件领域,近几年来二维过渡金属硫化物(TMDs)、硒化物,如MoS2、WS2、MoSe2、WSe2等,纷纷实现了晶圆尺寸制备,被各大顶刊报道 [1-6],应用于晶体管及逻辑电路制备,并有望减轻短沟道效应,这使得二维材料走出实验室推进实际应用又向前了一步。

近日,美国宾夕法尼亚州立大学Saptarshi Das教授联合斯坦福大学、杜克大学等多家研究机构的学者,在Nature Electronics 杂志上发表综述,系统回顾了二维场效应晶体管的发展历史,讨论了关键性能指标,并展望了基于二维晶体管在超大规模集成电路(very large-scale integration, VLSI)中的优势与挑战。

晶圆尺寸二维材料。[1-6]

发展历史

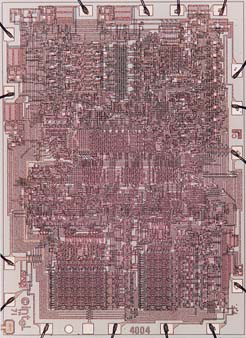

1971年11月,第一款商用微处理器——英特尔4004上市,至今已整整50年。这是一款4位CPU(4 bit),集成了约2300个晶体管,采用10 μm制程,最高主频只有740 kHz,尺寸3 mm × 4 mm,被嵌入到一个16针的封装中。五十年后,第12代英特尔CoreTM i7处理器由上百万晶体管组成,采用了10 nm工艺,最高主频可达5 GHz。五十年间,器件结构、制备方法、电路设计等方面都进行了无数次创新,然而,有一件事保持不变——硅,仍然是微电子产业的基础。

Inter 4004处理器。图片来源:Nat. Electron. [7]

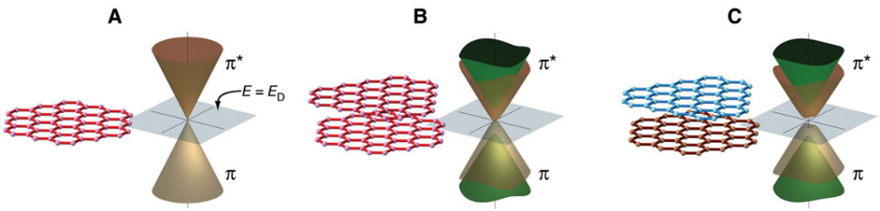

随着硅基器件即将达到摩尔定律极限,10 nm以下的工艺技术越来越具有挑战性。如果将场效应晶体管(FET)沟道宽度降低至亚1纳米范围,将使得沟道-电介质界面处电荷载流子散射急剧增加,并导致三维半导体晶体的迁移率严重降低。石墨烯——于2004年被剥离出来——这种二维材料具有高迁移率,不存在悬空键的单层结构有助于电子-空穴传输,抑制沟道-电介质界面散射。然而,如何将这种零带隙材料改性为半导体,又变成一项艰巨的任务。

石墨烯狄拉克点。图片来源:Science [8]

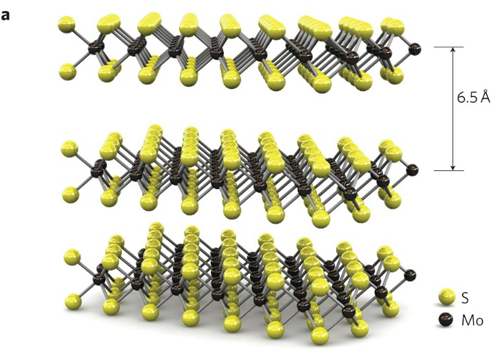

2008年,博士毕业不久的Andras Kis来到瑞士洛桑联邦理工学院工作。他决定带领课题组采取一种不同的方法:如果石墨烯很难变成半导体,那么为什么不直接利用一种本身就具有带隙的二维材料呢 [9]?于是,他们锁定了MoS2作为研究对象,并从辉钼矿中成功剥离出单层MoS2(直接带隙~1.8 eV),基于其制备的晶体管迁移率高达~200 cm2 V−1 s−1,该工作于2011年发表在Nature Nanotechnology 杂志上,论文标题言简意赅“Single-layer MoS2 transistors” [10],几个词就概况了论文的最大亮点,霸气十足!

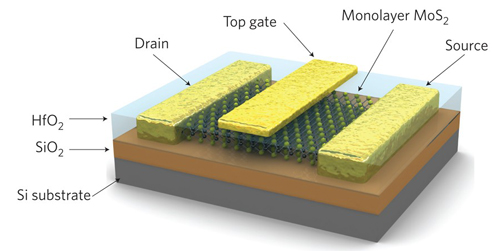

单层MoS2与晶体管器件示意图。图片来源:Nat. Nanotech. [10]

二维生长

尽管机械剥离具有简单、高效、快速试错等诸多优势,但这种策略制备成本及制成品尺寸的限制使其更适合发表论文,在实际工业生产中缺乏可行性。如果使TMDs应用于集成电路的制备,晶圆级合成是不可避免的,化学气相沉积(CVD)和金属-有机化学气相沉积(MOCVD)技术于是脱颖而出。不过,这些生长工艺温度通常大于500 °C,而根据International Roadmap for Devices and Systems(IRDS)建议的标准,CMOS工艺兼容性要求TMDs生长温度低于450 °C。目前报道的CVD方法通常将TMDs外延生长在蓝宝石基底上,这大大减少了晶界数量,同时避免了温度兼容性问题。但是,随之而来的第二个难题是,如何将其清洁且无损地转移,以及之后的光刻、沉积等过程中,如何在不破坏二维材料结构的前提下去除残留物,这些工艺设计往往会影响器件的性能。

基于二维材料的FET。图片来源:Nat. Electron.

晶体管构建

随着二维材料在晶体管中的应用,各种顶栅、底栅、分栅、全环绕栅极结构被制备并研究。开态电流(ION)、关态电流(IOFF)、电流开/关比、载流子迁移率(μ)、阈值电压(VTH)、亚阈值摆幅(SS)、接触电阻(RC)、饱和漂移速度(vSAT)等作为衡量器件性能的关键指标。值得注意的是,对于二维器件,载流子迁移率没有通常假设的那么重要,因为纳米级晶体管中的电流将