ACD是很明显采用随机存取方式。要注意CD-ROM它的访问方式是顺序访问,但是并不属于ROM

★★★

由于16MB=2 24 ^{24}24B,所以理应是2 24 ^{24}24,但是字长是32位,由于按照半字=2B寻址,所以单元数目就为2 23 ^{23}23个

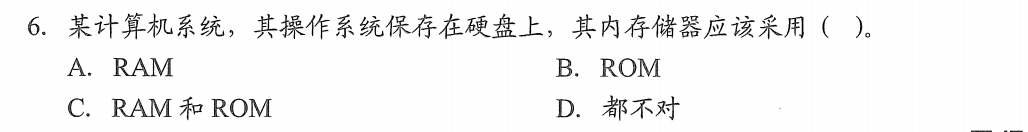

RAM是肯定的,但是一定注意ROM。BIOS中有引导程序,负责将操作系统引导至内存,它是固化在主板上的,属于ROM

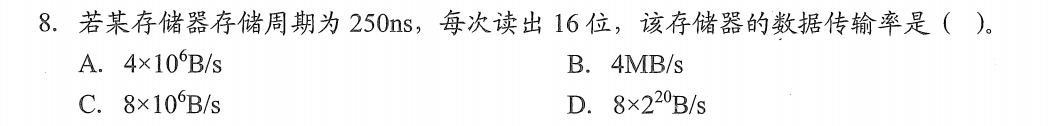

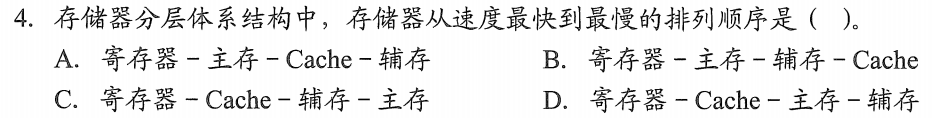

每次读出16bit=2B,所以数据传输率=2B/250×10− 9s10^{-9}s10−9s=答案【C】

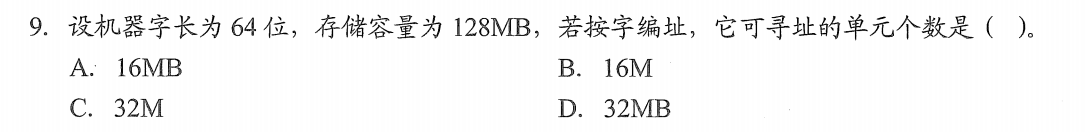

128MB/8B=16M

★★★

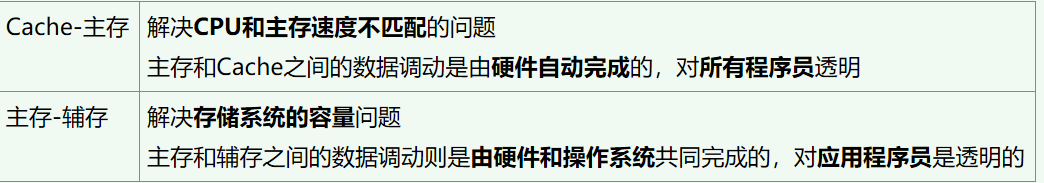

1024×8位,说明就是1024B,又因为210=1024,所以地址线需要10根 8位说明需要8根数据线 需要1根片选线 读写控制线2根

所以10+8+1+2=21根

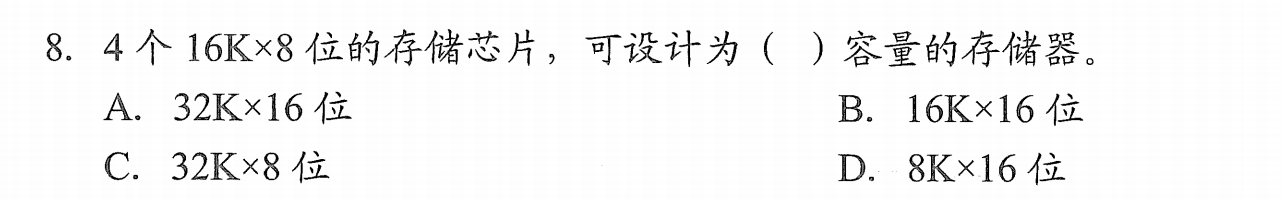

注意32K=215

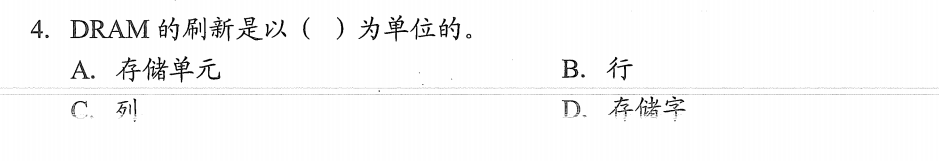

SRAM和DRAM的区别在于是否需要动态刷新

注意此题易选A,这里面选通线是两根,用于送行地址和列地址

★★★

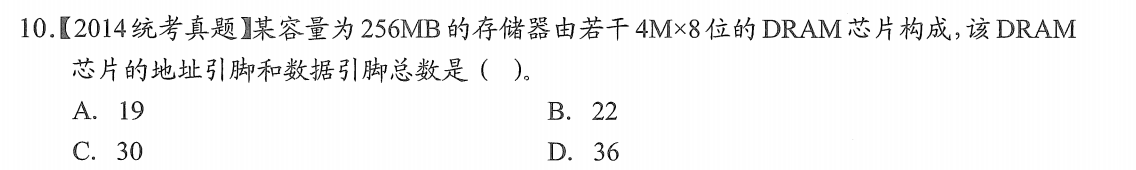

4M=222,由于DRAM采用地址线复用,所以只需要用11根,数据线为8根

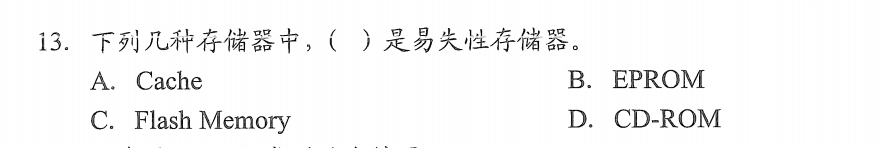

闪存可读可写,依然属于ROM,写入时由于需要先擦除原来的数据,所以写速度很慢

Cache属于易失性存储器(SRAM)

根据题意,ROM区大小为4KB,RAM区大小为60KB

那么ROM芯片数量为 4 K × 1 B 2 K × 1 B\frac{4K×1B}{2K×1B}2K×1B4K×1B=2

那么RAM芯片数量为 60 K × 1 B 4 K × 0.5 B\frac{60K×1B}{4K×0.5B}4K×0.5B60K×1B=30

.★★★

首先2个2K×4位芯片进行组成1个2K×8位的芯片(位扩展),最后4个2K×8位的芯片再组成1个8K×8位的芯片(字扩展)

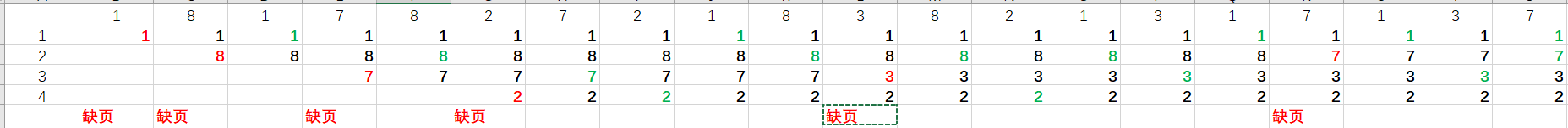

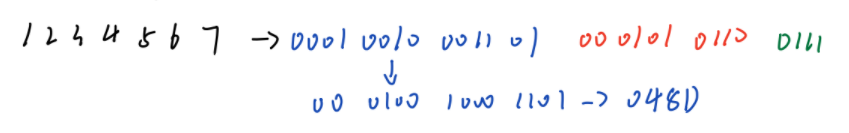

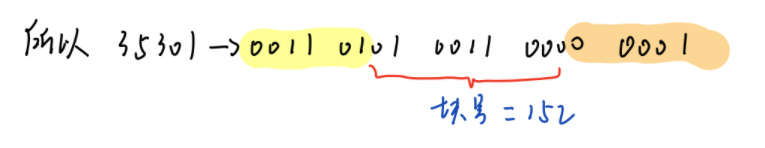

对于位扩展来说它不影响地址,只有字扩展影响。 因此0B1F=0000 1011 0001 1111。所以加粗部分的两位用于片选,有00、01、10、11四个选项,那么最小0B1F所在芯片的最小地址就是0000 1000 0000 000,即0800H

5FFFH-4000H+1=2000H=(8192) 10 _{10}10=2 13 ^{13}13。所以ROM区大小为8KB,那么RAM区大小就是56KB。因此 56 K × 1 B 8 K × 0.5 B\frac{56K×1B}{8K×0.5B}8K×0.5B56K×1B=14

主存地址空间大小为64MB,且64M=2 26 ^{26}26,所以是26位。需要注意实际的主存容量32MB不能代表MAR的位数

首先位扩展是肯定的。又因为它是以4B为编址单位的,所以不需要进行字扩展

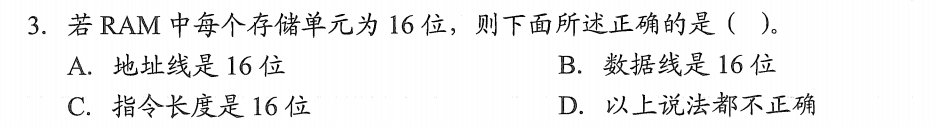

注意这里是按照字寻址,一个字为2B=16位

首先进行位扩展,用4个512k×8位的芯片组成1个512k×32位的芯片。接着进行字扩展,由于2 24 /2 19 =2 5 =322^{24}/2^{19}=2^{5}=32224/219=25=32。所以32×4=128片

解释如下

地址总线表明了最大的寻址范围,这里是16位。可以不必用完实际寻址范围则由具体芯片数目䦺由于是4K×4位,且2 12= 4 K 2^{12}=4K212=4K,说明地址线为12,数据线为42个4K×4位进行位扩展形成1个4k×8位的芯片,然后再进行4扩展。所以总共需要8个芯片,有4组因此这4组至少需要两位才能片选,,所以低12位为片内地址,相应的,A 2 A 3A_{2}A_{3}A2A3进行片选

43FFH=4000H+1=400H=2 10 =1K^{10}=1K10=1K,每个存储单元为2B。由于 1 K × 2 B 256 × 2 B\frac{1K×2B}{256×2B}256×2B1K×2B=4.所以选项C正确

CFFFFH-90000H=40000H=2 18 2^{18}218=256K,因此 256 K × B 16 K × 1 B\frac{256K×B}{16K×1B}16K×1B256K×B=16

由于23K=2 15 2^{15}215,所以片内地址是15位,那么首地址就是0011 1000 0000 0000 0000=3800H,末地址就是3FFFFH

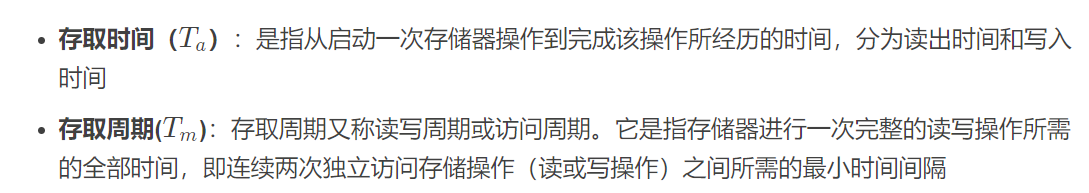

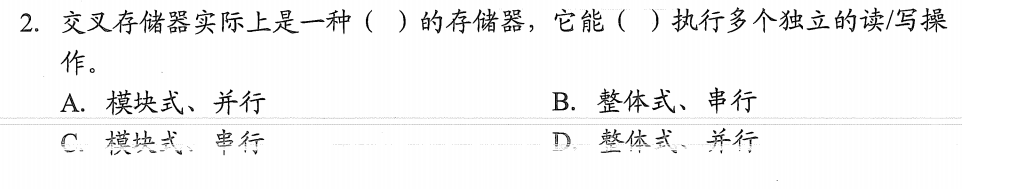

只有大于等于才能保证第二次启动某存储体时,其存取周期能结束

在存取周期200ns内可以连续的访问四个模块

由于高位地址在单个存储器是连续的,所以需要恢复,不能很慢的满足局部性原理

double类型的变量占8B,64位,所以需要读8次

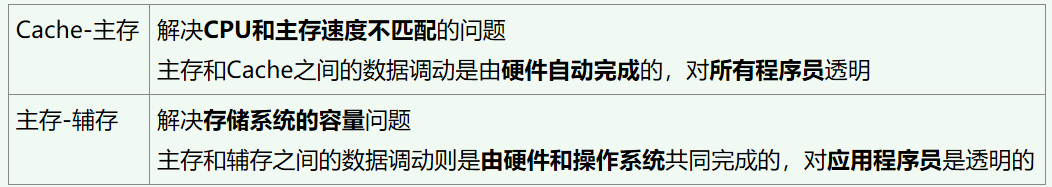

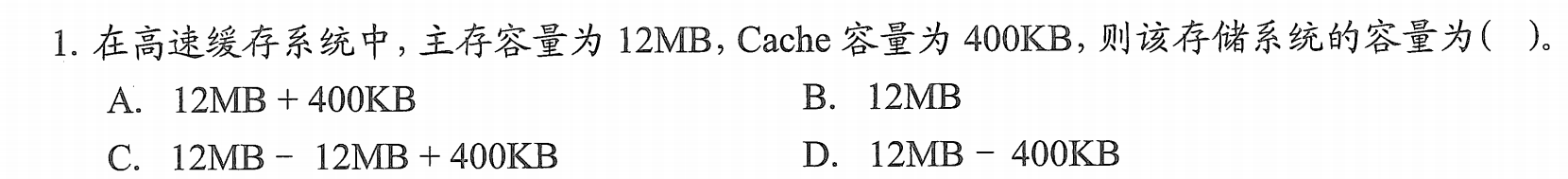

注意Cache中仅是主存数据的副本

★★★

由题意可知共分为8组,组号从0到7,每个主存块的大小为32B。因此129号单元所处主存块号为4,由于4%8=4,所以组号为4

所谓失效就是指写不命中

★★★

一个块有多个字(通常)组成,CPU与Cache或主存交换的单位是字,Cache与主存交换单位是块,当CPU想要访问的某个字不再Cache中时,会将该字所在主存块调入Cache中

块内地址由Cache容量决定,16KB=2 14 ^{14}14B,所以低14位要作为块内地址

主存容量与Cache容量的比值可以确定块号范围,也即需要用12位,由于还需要一位有效位,所以是13位

★★★

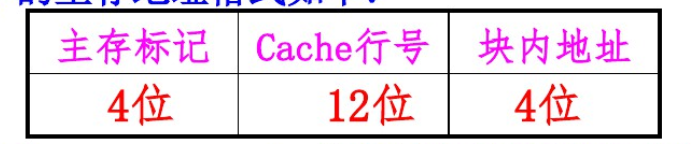

128KB/16B=8K,所以有8K个Cache行,也即2 13 2^{13}213个,由于8路组相连,所以是2 10 2^{10}210组,所以主存块号的中间10位用于标记组号,由于每块16B,所以块内地址需要用4位标记

★★★

1024KB除以16KB=2 6 2^{6}26,所以需要6位标记块号。 每块有8字,每字32bit,也即4B,所以每块32B,因此需要用5位标记块内地址

1.设有一个具有20位地址和32位字长的存储器,问 (1)该存储器能存储多少字节的信息? (2)如果存储器由512K×8位的SRAM芯片组成,需要多少片 (3)需要多少位作芯片选择

解答:

(1)地址有20bit,那么就有2 20 2^{20}220个,每个存储单元字长为32位=4B。所以可以存储2 22 2^{22}222B,约为4M

(2)

首先进行位扩展,每个4个SRAM芯片组成一个512K×32位的SRAM芯片,为一组2 202^{20}220=1024K,所以 1024K×32bit512K×32bit\frac{1024K× 32bit}{512K×32bit}512K×32bit1024K×32bit=2。共需要2组,也即需要8片(3)位扩展是不影响地址的,只有字扩展需要,其实相当于“2”个芯片。所以只需一位即可

2.已知某64位主机采用半导体存储器,其地址码为26位,若使用4M×8位的DRAM芯片组成该机所允许的最大主存空间,并选用内存条结构形式,问 (1)若每个内存条为16M×64位,共需要多少内存条 (2)每个内存条共有多少DRAM芯片 (3)主存共需要多少DRAM芯片? (4)CPU如何选择各内存条

解答

(1)16M=2 4 2^{4}24M=2 24 2^{24}224bit,因此共需要 2 26 2 24\frac{2^{26}}{2^{24}}224226=4根,所以共需要4根内存条 (2)由于 16 M × 8 B 4 M × 1 B\frac{16M×8B}{4M×1B}4M×1B16M×8B=32,所以需要32片 (3)

共需要128片

这里共有4根内存条。每个内存条是16M×64位,所以需要24根地址线作为内地址,同时需要2位用于选择内存条。通过2,4译码器对各内存条进行选择

3.用16K×8位的DRAM芯片构成64K×32位存储器 (1)画出存储器的组成逻辑图 (2)设存储器读/写周期为0.5us,CPU在1us内至少要访问一次。试问采用何种刷新方式合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间多少?

解答

(1)由于 64 K × 32 位 16 K × 8 位\frac{64K×32位}{16K×8位}16K×8位64K×32位=16,所以共需要16片DRAM芯片。其中每4片为一组进行位扩展,共有4组,然后这4组再进行字扩展。因此就有4个模块,需要用2位进行片选,且16K=2 14 2^{14}214,所以每个模块的地址空间需要用14位。故地址总线16位,使用2,4译码器进行选择

(2)假设DRAM内部结构排列形式为128×128,存储周期为0.5us,电容最多坚持2ms,因此对应2ms/0.5us=4000个周期,因此有128行,刷新每一行都需要0.5us

(2)假设DRAM内部结构排列形式为128×128,存储周期为0.5us,电容最多坚持2ms,因此对应2ms/0.5us=4000个周期,因此有128行,刷新每一行都需要0.5us

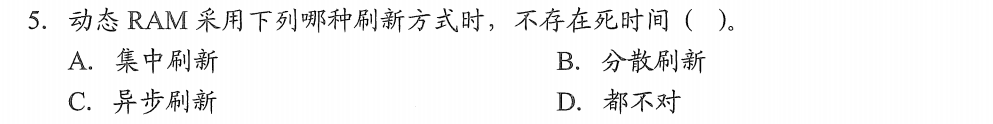

如果采用集中刷新,刷新128行需要使用128个周期,也就是说至少存在64us的死时间,肯定不符合题意

如果采用分散刷新,则每1us只能访存一次,也不行

所以采用异步。刷新间隔2ms/128=15.6us。因此每15.6us会产生一次刷新信号(可取15us)。所以实际刷新时间为15us×128=1.92ms

4.有一个1024K×32位的存储器,由128K× 8位的DRAM芯片构成 (1)总共需要多少DRAM芯片 (2)设计此存储体的组成框图 (3)采用异步刷新方式,如果单元刷新间隔不超过8ms,则刷新信号周期多少?

解答:

(1)由于 1024 K × 32 位 128 K × 8 位\frac{1024K×32位}{128K×8位}128K×8位1024K×32位=8×4=32,所以需要32片DRAM芯片 (2)首先每4片为一组进行位扩展,共计8组,然后这8组进行字扩展。需要使用3,8译码器。由于2 17 2^{17}217=128K,因此每一组片内地址需要用17位,即A 0 −A 16 A_{0}-A_{16}A0−A16,然后A 17 −A 19 A_{17}-A_{19}A17−A19进行片选

(3)如果选择一个行地址进行刷新,刷新地址为A 0 −A 8 A_{0}-A_{8}A0−A8。因此这一行上的2048个存储元同时刷新,也即在8ms内进行512周期。刷新方式采用

(3)如果选择一个行地址进行刷新,刷新地址为A 0 −A 8 A_{0}-A_{8}A0−A8。因此这一行上的2048个存储元同时刷新,也即在8ms内进行512周期。刷新方式采用

5.

解答:

由于 1024 K × 32 位 256 K × 16 位\frac{1024K×32位}{256K×16位}256K×16位1024K×32位=4×2=8,需要使用8片。其中每两片为一组进行位扩展,分为4组,然后进行字扩展。需要使用2,4译码器。由于2 18 ^{18}18=256k。所以A 0 −A 17 A_{0}-A_{17}A0−A17作为片内地址,A 18 −A 19 A_{18}-A_{19}A18−A19进行片选

6.用32K×8位的E 2P R O M E^{2}PROME2PROM芯片组成128K×16位的只读存储器,问 (1)MAR多少位 (2)MDR多少位 (3)共需要多少E 2P R O M E^{2}PROME2PROM芯片 (4)画出组成框图

解答

(1)由于128K=2 17 128K=2^{17}128K=217,所以MAR17位 (2)MDR16位 (3)共需要8片 (4)

7 (1)画出地址译码方案 (2)将ROM与RAM同CPU连接

(1)画出地址译码方案 (2)将ROM与RAM同CPU连接

解答 (1)ROM区域地址范围为0000H~3FFFH,由于3FFFH-0000H+1=4000H=2 14 2^{14}214,因此ROM区域大小为16KB。由题意,共需要 40 K × 16 位 8 K × 8 位=5×2\frac{40K×16位}{8K×8位}=5×28K×8位40K×16位=5×2=10片。每两片进行扩展,共有5组,使用3,8译码器

(2)

★★★

8.

解答

顺序存储器和交叉存储器连续读出8个字,其总位数为512bit

顺序存储器时间:t 1t_{1}t1=8×100ns= 8 × 10−7s 8×10^{-7}s8×10−7s交叉存取器时间:t 2t_{2}t2=T+(m-1) τ \tauτ=100+7×50= 4.5 × 10−7s 4.5×10^{-7}s4.5×10−7s带宽分别为

顺序存储器:W 1=5128×10− 7 = 64 × 10 7b i t / s W_{1}=\frac{512}{8×10^{-7}}=64×10^{7} bit/sW1=8×10−7512=64×107bit/s交叉存储器:W 2=5124.5×10− 7 s= 113.8 × 10 7b i t / s W_{2}=\frac{512}{4.5×10^{-7}s}=113.8×10^{7} bit/sW2=4.5×10−7s512=113.8×107bit/s9

解答:

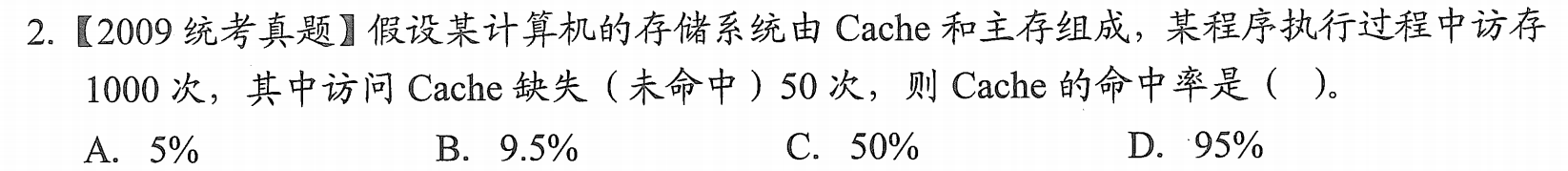

命中率 H HH= HcNc+Nm=24202420+80= 0.968 \frac{H_{c}}{N_{c}+N_{m}}=\frac{2420}{2420+80}=0.968Nc+NmHc=2420+802420=0.968cache-主存系统的平均访问时间t a= ht c+ ( 1 − h )t mt_{a}=ht_{c}+(1-h)t_{m}ta=htc+(1−h)tm,其中 ( 1 − h ) (1-h)(1−h)和t mt_{m}tm分别表示缺失率和主存访问时间,因此t a= 0.968 × 40 + 0.032 × 240 = 46.4 t_{a}=0.968×40+0.032×240=46.4ta=0.968×40+0.032×240=46.4效率为40/46.4=86.2%10

解答

由t a =ht c +(1−h)t m t_{a}=ht_{c}+(1-h)t_{m}ta=htc+(1−h)tm可知,h=ta −tmtc −tm= 50 − 200 40 − 200=93.75h=\frac{t_{a}-t_{m}}{t_{c}-t_{m}}=\frac{50-200}{40-200}=93.75h=tc−tmta−tm=40−20050−200=93.75%

11

解答

不相等

12

解答

T a =HT 1 +(1−H)T 2 T_{a}=HT_{1}+(1-H)T_{2}Ta=HT1+(1−H)T2

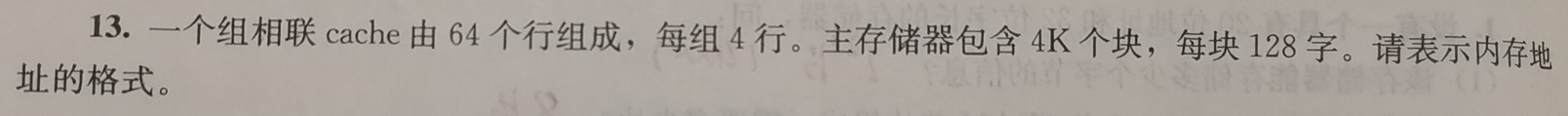

13

解答

Cache有64行,每组4行,需要4位确定组号每块有128个地址,所以需要7位确定块内地址由于主存有4K个块,所以需要12位,其后4位正好作为组号标记

14

解答:

主存容量与Cache容量之比可以确定块号范围。所以比值是16,所以需要16位Cache容量64KB,块大小为16B,所以块的个数需要用12位标记(用16位的后12位)字长为1B,说明一个块有16个地址,那么块内地址需要4位标记